# **MCP Specification**

2Gb SLC NAND Flash (X8) + 2Gb LPDDR2 (X32)

Nanya Technology Corporation

All Rights Reserved. ©

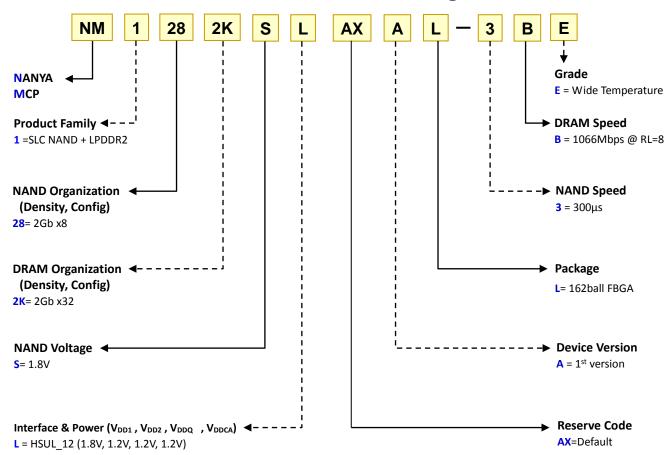

# **Ordering Information**

| MCP                              |      | NA                             | ND              |               |        | DRAM                           |       |    |

|----------------------------------|------|--------------------------------|-----------------|---------------|--------|--------------------------------|-------|----|

| Part Number                      | Туре | Density<br>(Org.)              | Program<br>Time | Erase<br>Time | Туре   | Density<br>(Org.)              | Speed | RL |

| NM1 <mark>2</mark> 82KSLAXAL-3BE | SLC  | <b>2Gb</b> (256Mb <b>X 8</b> ) | 300µs           | 3.5ms         | LPDDR2 | <b>2Gb</b> (64Mb <b>X 32</b> ) | 1066  | 8  |

# **NANYA MCP Part Numbering Guide**

Version 1.3 3 Nanya Technology Corp. 06/2018 All Rights Reserved. ©

### **Features**

#### **MCP**

- Separate SLC NAND and LPDDR2 RAM interfaces

- Lead-free (RoHS compliant) and Halogen-free Package: 162-ball VFBGA 8.00 x 10.50 x 1.00 (mm)

- Operating temperature range: -40°C to +85°C

#### **2Gb X8 SLC NAND**

Voltage Supply(VCC/VCCQ): 1.70V ~ 1.95V

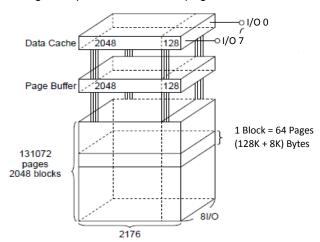

#### Organization

- Memory Cell Array: 2176 x 128K x 8

- Register: 2176 x 8 - Page Size: 2176 Bytes

- Block Erase Size: (128K + 8K) Bytes

#### Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

#### **Mode control**

- Serial input/output

- Command control

#### Number of valid blocks

- Min 2008 blocks

- Max 2048 blocks

#### Access time

- Cell array to register: 25µs max

- Serial Read Cycle: 25ns min (CL=30pF)

#### Program/Erase time

- Auto Page Program: 300µs/page typical

- Auto Block Erase: 3.5ms/block typical

#### Operating current

- Read (25ns cycle): 30 mA max - Program (avg.): 30 mA max

- Erase (avg.): 30 mA max

- Standby: 50 µA max

8 bit ECC for each 512 Bytes is required.

#### 2Gb X32 LPDDR2

#### • Speed, Addressing and Retention Specification

| 64Mb x 32   |

|-------------|

| 1066 / RL=8 |

| S4B         |

| 8           |

| BA0-BA2     |

| R0-R13      |

| C0-C8       |

| 3.9         |

|             |

#### JEDEC LPDDR2 Compliant

- Low Power Consumption

- Double-data rate on DQs, DQS, DM and CA bus

- 4n Prefetch Architecture

#### HSUL12 interface and Power Supply

- VDD1= 1.70 to 1.95V

- VDD2/VDDQ/VDDCA = 1.14 to 1.3V

#### Signal Integrity

- Configurable DS for system compatibility

- ZQ calibration for the accuracy of output driver strength over Process, Voltage and Temperature

#### Training for Signals' Synchronization

- DQ Calibration offering specific DQ output patterns

#### Data Integrity

- DRAM built-in Temperature Sensor for Temperature Compensated Self Refresh (TCSR)

- Auto Refresh, Self Refresh and PASR Modes

#### Power Saving Modes

- Deep Power Down Mode (DPD)

- Partial Array Self Refresh (PASR)

- Clock Stop capability during idle period

#### **Programmable Function**

- Output Drive Impedance (34.3/40/48/60/80/120)

- Burst Lengths (4/8/16)

- Burst Type (Sequential/Interleaved)

- Read Latency (3/4/5/6/7/8), Write Latency (1/2/3/4)

- nWR (3/4/5/6/7/8)

# Ball Assignment - (162b Flash X 8 + DRAM X 32)

Part Number: NM1282KSLAXAL-XXX

### Top View, A1 in Top Left Corner

| _ |       |       |        |     |      |       |       |      |        | _    | _ |

|---|-------|-------|--------|-----|------|-------|-------|------|--------|------|---|

| • | 1     | 2     | 3      | 4   | 5    | 6     | 7     | 8    | 9      | 10   |   |

| Α | DNU   | DNU   | WP     | CLE | VCC  | I/O 4 | I/O 7 | VCC  | DNU    | DNU  | Α |

| В | DNU   | VCC   | NC     | ALE | RE   | I/O 5 | NC    | NC   | VSS    | DNU  | В |

| С | NC    | I/O 1 | I/O 3  | WE  | R/B  | I/O 6 | NB    | NB   | NB     | NB   | С |

| D | NC    | I/O 0 | I/O 2  | CE  | NC   | NC    | NB    | NB   | NB     | NB   | D |

| E | VSS   | NC    | NC     | NB  | VDD2 | VDD1  | DQ31  | DQ29 | DQ26   | DNU  | Ε |

| F | VDD1  | VSS   | NC     | NB  | VSS  | VSS   | VDDQ  | DQ25 | VSS    | VDDQ | F |

| G | VSS   | VDD2  | ZQ     | NB  | VDDQ | DQ30  | DQ27  | DQS3 | DQS3   | VSS  | G |

| Н | VSS   | CA9   | CA8    | NB  | DQ28 | DQ24  | DM3   | DQ15 | VDDQ   | VSS  | н |

| J | VDDCA | CA6   | CA7    | NB  | VSS  | DQ11  | DQ13  | DQ14 | DQ12   | VDDQ | J |

| K | VDD2  | CA5   | VREFCA | NB  | DQS1 | DQS1  | DQ10  | DQ9  | DQ8    | VSS  | K |

| L | VDDCA | VSS   | CK     | NB  | DM1  | VDDQ  | NB    | NB   | NB     | NB   | L |

| М | VSS   | NC    | CK     | NB  | VSS  | VDDQ  | VDD2  | VSS  | VREFDQ | NB   | M |

| N | CKE   | NC    | NC     | NB  | DM0  | VDDQ  | NB    | NB   | NB     | NB   | N |

| Р | CS    | NC    | NC     | NB  | DQS0 | DQS0  | DQ5   | DQ6  | DQ7    | VSS  | P |

| R | CA4   | CA3   | CA2    | NB  | VSS  | DQ4   | DQ2   | DQ1  | DQ3    | VDDQ | R |

| Т | VSS   | VDDCA | CA1    | NB  | DQ19 | DQ23  | DM2   | DQ0  | VDDQ   | VSS  | Т |

| U | VSS   | VDD2  | CA0    | NB  | VDDQ | DQ17  | DQ20  | DQS2 | DQS2   | VSS  | U |

| V | VDD1  | VSS   | NC     | NB  | VSS  | VSS   | VDDQ  | DQ22 | VSS    | VDDQ | ٧ |

| W | DNU   | NC    | NC     | NB  | VDD2 | VDD1  | DQ16  | DQ18 | DQ21   | DNU  | W |

| Υ | DNU   | DNU   | NB     | NB  | NB   | NB    | NB    | NB   | DNU    | DNU  | Υ |

|   | 1     | 2     | 3      | 4   | 5    | 6     | 7     | 8    | 9      | 10   | • |

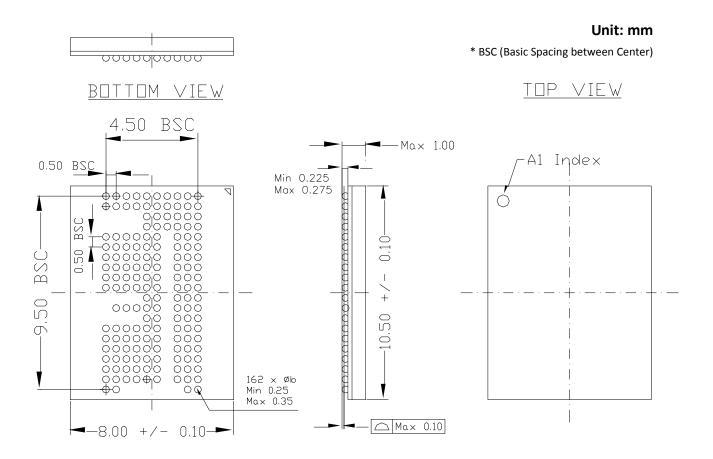

# Package Outline Drawing (8.00mm x 10.50mm x 1.00mm)

# **Ball Description - 2Gb X8 SLC NAND**

| Symbol              | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X8: <b>I/O[7:0]</b> | Input/output | <b>Data Bus:</b> The I/O0 to 7 pins are used as a port for transferring address, command and input/output data to and from the device.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLE                 | Input        | Command Latch Enable: The CLE input signal is used to control loading of the operation mode command into the internal command register. The command is latched into the command register from the I/O port on the rising edge of the WE signal while CLE is High.                                                                                                                                                                                                                                                                                                               |

| ALE                 | Input        | Address Latch Enable: The ALE signal is used to control loading address information into the internal address register. Address information is latched into the address register from the I/O ports on the rising edge of WE while ALE is High.                                                                                                                                                                                                                                                                                                                                 |

| CE                  | Input        | Chip Enable: The device goes into a low-power Standby mode when $\overline{CE}$ goes High during the device is in Ready state. The $\overline{CE}$ signal is ignored when device is in Busy state (RY / $\overline{BY}$ = L), such as during a Program or Erase or Read operation, and will not enter Standby mode even if the $\overline{CE}$ input goes High.                                                                                                                                                                                                                 |

| RE                  | Input        | Read Enable: The RE signal controls serial data output. Data is available tREA after the falling edge of RE.  The internal column address counter is also incremented (Address = Address +1) on this falling edge.                                                                                                                                                                                                                                                                                                                                                              |

| WE                  | Input        | <b>Write Enable:</b> The WE signal is used to control the acquisition of data from the I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WP                  | Input        | <b>Write Protect:</b> The $\overline{WP}$ signal is used to protect the device from accidental programming or erasing. The internal voltage regulator is reset when $\overline{WP}$ is Low. This signal is usually used protecting the data during the power-on/off sequence when input signals are invalid.                                                                                                                                                                                                                                                                    |

| RY/BŸ               | Output       | <b>Ready / Busy Output:</b> The RY / $\overline{BY}$ output signal is used to indicate the operation condition of the device. The RY / $\overline{BY}$ signal is in Busy state (RY / $\overline{BY}$ =L) during the Program, Erase and Read operations and will return to Ready state (RY / $\overline{BY}$ =H) after completion of the operation. The output buffer for this signal is an open drain and has to be pulled-up to Vccq with an appropriate resister.  If RY / $\overline{BY}$ signal is not pulled-up to Vccq ("Open" state), device operation cannot guarantee. |

| VCC                 | Supply       | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VSS                 | Supply       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NC                  | _            | No Connect: These pins should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **Ball Description** - 2Gb X32 LPDDR2

| Symbol           | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ск, ск           | Input        | Clock: CK and $\overline{\text{CK}}$ are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK. Single Data Rate (SDR) inputs, $\overline{\text{CS}}$ and CKE, are sampled at the positive Clock edge. Clock is defined as the differential pair, CK and $\overline{\text{CK}}$ . The positive Clock edge is defined by the crosspoint of a rising CK and a falling $\overline{\text{CK}}$ . The negative Clock edge is defined by the crosspoint of a falling CK and a rising $\overline{\text{CK}}$ . |

| CKE              | Input        | Clock Enable: CKE high activates, and CKE low deactivates internal clock signals, and device input buffers and output drivers. Power saving modes are entered and exited through CKE transitions. CKE is considered part of the command code. CKE is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                               |

| <del>CS</del>    | Input        | Chip Select: $\overline{\text{CS}}$ is considered part of the command code. $\overline{\text{CS}}$ is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CA0 – CA9        | Input        | Command/Address Inputs: Uni-directional command/address bus inputs. Provide the command and address inputs according to the command truth table. CA is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                            |

| DM0 – DM3        | Input        | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS.  Although DM pins are input-only, the DM loading matched the DQ and DQS (or DQS).  DM0 corresponds to the data on DQ0-DQ7, DM1 corresponds to the data on DQ8-DQ15, DM2 corresponds to the data on DQ16-DQ23, and DM3 corresponds to the data on DQ24-DQ31.                                                                                                        |

| DQ0-DQ31         | Input/output | Data Bus: Bi-directional Input / Output data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQS0-3, DQS0-3   | Input/output | Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and Differential (DQS and $\overline{DQS}$ ). It is output with read data and input with write data. DQS is edge-aligned to read data, and centered with write data.  DQS0 & $\overline{DQS0}$ corresponds to the data on DQ0-DQ7, DQS1 & $\overline{DQS1}$ corresponds to the data on DQ8-DQ15, DQS2 & $\overline{DQS2}$ corresponds to the data on DQ16-DQ23, DQS3 & $\overline{DQS3}$ corresponds to the data on DQ24-DQ31.                            |

| NC               | _            | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ZQ               | Input        | Reference Pin for Output Drive Strength Calibration. External impedance (240-ohm): this signal is used to calibrate the device output impedance.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD1</sub> | Supply       | Core Power Supply 1: Core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD2             | Supply       | Core Power Supply 2: Core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDDQ             | Supply       | DQ Power Supply: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDCA            | Supply       | Input Receiver Power Supply: Power supply for CA0-9, CKE, CS, CK, and CK input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VREFDQ, VREFCA   | Supply       | Reference Voltage: VREFDQ is reference for DQ input buffers. VREFCA is reference for Command / Address input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vss              | Supply       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

NOTE 1: The signal may show up in a different symbol but it indicates to the same thing. e.g.,  $/CK = CK\# = \overline{CK} = CKb$ ,  $/DQS = DQS\# = \overline{DQS} = DQSb, /CS = CS\# = \overline{CS} = CSb.$

Version 1.3 8 Nanya Technology Corp. 06/2018

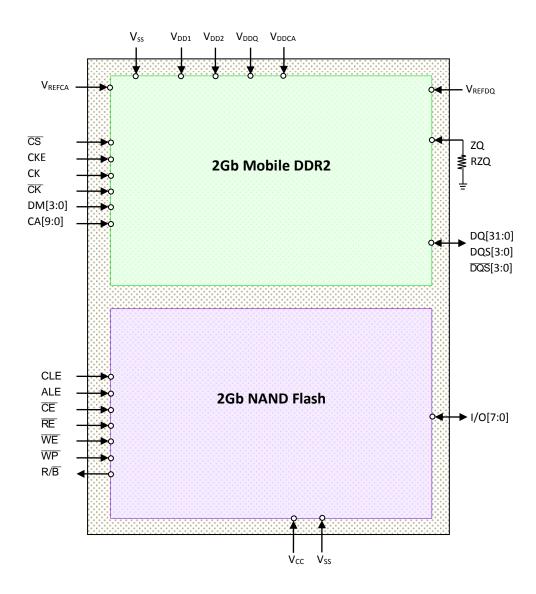

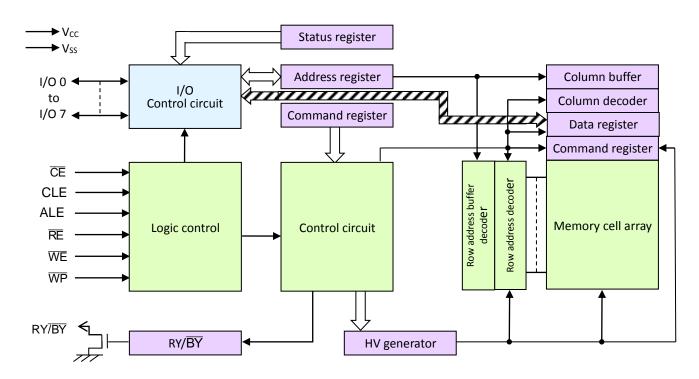

### **Functional Block Diagram**

# 2Gb(X8) SLC NAND Flash

### **Descriptions**

The device is a single 1.8V 2Gbit (2,281,701,376 bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E<sup>2</sup>PROM) organized as X8: (2048 + 128) bytes x 64 pages x 2048blocks.

The device has 2176-bytes static registers which allow program and read data to be transferred between the register and memory cell array in 2176-bytes increments. The Erase operation is implemented in a single block unit (X8=128 Kbytes + 8K bytes: 2176 bytes x 64 pages).

The device is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for command inputs. The Erase and program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density non-volatile memory data storage.

### **Function Block Diagram (X8)**

### **Schematic Cell Layout and Address Assignment (X8)**

The Program operation works on page units while the Erase operation works on block units

A page consists of 2176 bytes in which 2176 bytes are used for main memory storage and 128 bytes are for redundancy or for other uses.

1 Page = 2176 Bytes

1 Block = 2176 Bytes x 64 Pages = (128K + 8K) Bytes Capacity = 2176 Bytes × 64 Pages × 2048 Blocks

### Array Address (X8)

|                       | I/O 0            | I/O 1           | I/O 2            | I/O 3            | I/O 4           | I/O 5            | I/O 6            | I/O 7            | Address        |

|-----------------------|------------------|-----------------|------------------|------------------|-----------------|------------------|------------------|------------------|----------------|

| 1 <sup>st</sup> cycle | CA <sub>0</sub>  | CA <sub>1</sub> | CA <sub>2</sub>  | CA <sub>3</sub>  | CA <sub>4</sub> | CA <sub>5</sub>  | CA <sub>6</sub>  | CA <sub>7</sub>  | Column Address |

| 2 <sup>nd</sup> cycle | CA <sub>8</sub>  | $CA_9$          | CA <sub>10</sub> | CA <sub>11</sub> | L               | L                | L                | L                | Column Address |

| 3 <sup>rd</sup> cycle | $PA_0$           | $PA_1$          | $PA_2$           | $PA_3$           | $PA_4$          | PA <sub>5</sub>  | $PA_6$           | PA <sub>7</sub>  | Page Address   |

| 4 <sup>th</sup> cycle | PA <sub>8</sub>  | $PA_9$          | PA <sub>10</sub> | PA <sub>11</sub> | $PA_{12}$       | PA <sub>13</sub> | PA <sub>14</sub> | PA <sub>15</sub> | Page Address   |

| 5 <sup>th</sup> cycle | PA <sub>16</sub> | L               | L                | L                | L               | L                | L                | L                | Page Address   |

PA6 to PA16: Block address PAO to PA5: NAND address in block

# **Absolute Maximum Ratings**

| Symbol           | Rating                               | Value                     | Unit |  |

|------------------|--------------------------------------|---------------------------|------|--|

| Vcc              | Power Supply Voltage                 | -0.6 to +2.5              |      |  |

| Vin              | Input Voltage                        | -0.6 to +2.5              | V    |  |

| V <sub>I/O</sub> | Input / Output Voltage               | -0.6 to Vcc + 0.3 (≤2.5V) |      |  |

| PD               | Power Dissipation                    | 0.3                       | W    |  |

| Tsolder          | DER Soldering Temperature (10 s) 260 |                           | °С   |  |

| T <sub>STG</sub> | Storage Temperature                  | -55 to +125               | °C   |  |

# Capacitance<sup>1</sup>

(T<sub>A</sub>=25 $^{\circ}$ C, f=1.0MHz)

| Symbol          | Parameter | <b>Test Condition</b> | Min | Max | Unit |

|-----------------|-----------|-----------------------|-----|-----|------|

| C <sub>IN</sub> | Input     | V <sub>IN</sub> =0V   | _   | 10  | pF   |

| Соит            | Output    | V <sub>OUT</sub> =0V  | _   | 10  | pF   |

NOTE 1 This parameter is periodically sampled and is not tested for every device.

### **Valid Blocks**

| Symbol | Parameter              | Min   | Тур. | Max   | Unit   |

|--------|------------------------|-------|------|-------|--------|

| Nvb    | Number of Valid Blocks | 2,008 | _    | 2,048 | Blocks |

NOTE 1 The device occasionally contains unusable blocks.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over lifetime.

The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

## **Recommended DC Operating Conditions**

| Symbol | Parameter                | Min               | Тур. | Max       | Unit |

|--------|--------------------------|-------------------|------|-----------|------|

| Vcc    | Power Supply Voltage     | 1.70              | _    | 1.95      | V    |

| Vıн    | High Level Input Voltage | Vcc x 0.8         | _    | Vcc + 0.3 | V    |

| VIL    | Low Level Input Voltage  | -0.3 <sup>1</sup> | _    | Vcc x 0.2 | V    |

Note 1 -2V (pulse width lower than 20 ns)

### **DC and Operation Characteristics**

$(Ta = -25 \text{ to } 85^{\circ}\text{C}, V_{CC} = 1.70 \text{ to } 1.95\text{V})$

| Symbol          | Parameter                     | Test Conditions                                                                                          | Min       | Тур. | Max | Unit |

|-----------------|-------------------------------|----------------------------------------------------------------------------------------------------------|-----------|------|-----|------|

| l <sub>IL</sub> | Input Leakage Current         | V <sub>IN</sub> =0 to V <sub>CC</sub>                                                                    | _         | _    | ±10 | μA   |

| ILO             | Output Leakage Current        | V <sub>OUT</sub> =0 to V <sub>CC</sub>                                                                   | _         | _    | ±10 | μA   |

| Icco1           | Serial Read Current           | CE=V <sub>IL</sub> ,I <sub>OUT</sub> = 0 mA, tcycle=25ns                                                 | _         | _    | 30  | mA   |

| Icco2           | Programming Current           | _                                                                                                        | _         | _    | 30  | mA   |

| Іссоз           | Erasing Current               | _                                                                                                        | _         | _    | 30  | mA   |

| Iccs            | Standby Current               | $\overline{\text{CE}} = V_{\text{CC}} - 0.2 \text{ V}, \overline{\text{WP}} = 0 \text{ V/V}_{\text{CC}}$ | _         | _    | 50  | μΑ   |

| Vон             | High Level Output Voltage     | I <sub>OH</sub> = -0.1mA                                                                                 | Vcc - 0.2 | _    | _   | V    |

| Vol             | Low Level Output Voltage      | $I_{OL} = 0.1 \text{mA}$                                                                                 | _         | _    | 0.2 | V    |

| Iol (RY/BY)     | Output Current of (RY/BY) pin | V <sub>OL</sub> =0.2V                                                                                    | _         | 4    | _   | mA   |

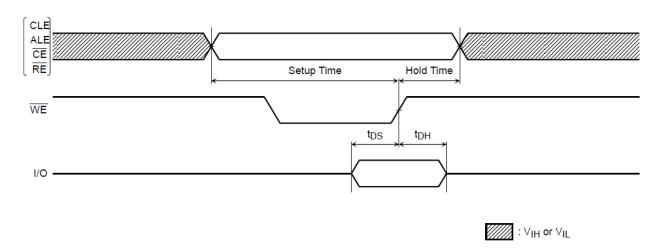

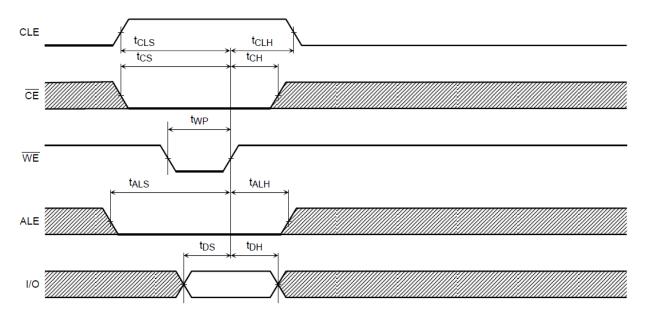

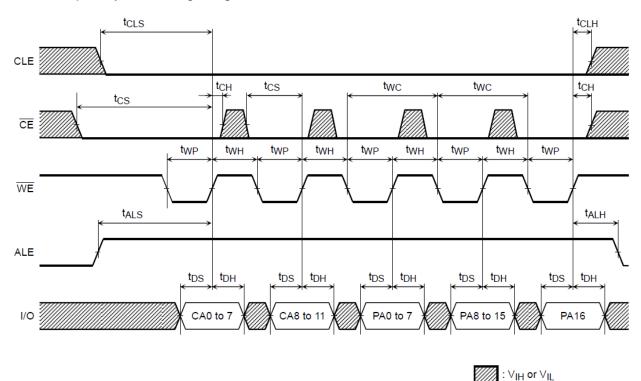

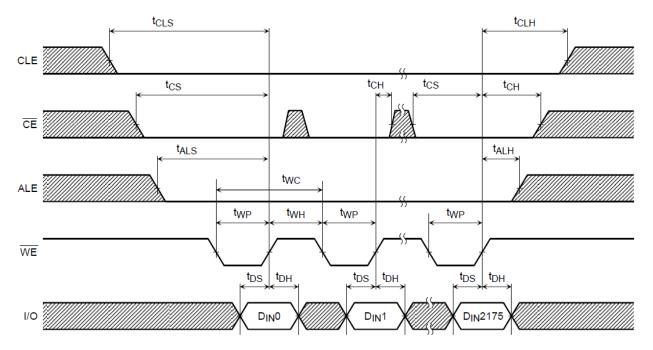

# **AC Characteristics and Recommended Operating Conditions**

(Ta= -25 to 85°C, Vcc=1.70 to 1.95V)

| Symbol | Parameter         | Min | Max | Unit |

|--------|-------------------|-----|-----|------|

| tCLS   | CLE Setup Time    | 12  | _   | ns   |

| tCLH   | CLE Hold Time     | 5   | _   | ns   |

| tCS    | CE Setup Time     | 20  | _   | ns   |

| tCH    | CE Hold Time      | 5   | _   | ns   |

| tWP    | Write Pulse Width | 12  | _   | ns   |

| tALS   | ALE Setup Time    | 12  | _   | ns   |

| tALH   | ALE Hold Time     | 5   | _   | ns   |

| tDS    | Data Setup Time   | 12  | _   | ns   |

| tDH    | Data Hold Time    | 5   | _   | ns   |

| tWC    | Write Cycle Time  | 25  | _   | ns   |

| tWH    | WE High Hold Time | 10  | _   | ns   |

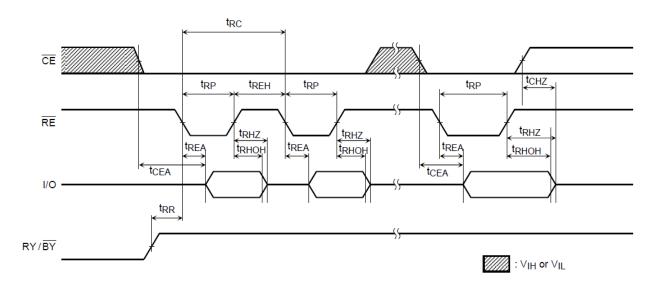

### **AC Characteristics for Operation**

| Symbol   | Parameter                                                 | Min | Max | Unit |  |  |  |

|----------|-----------------------------------------------------------|-----|-----|------|--|--|--|

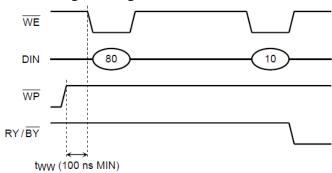

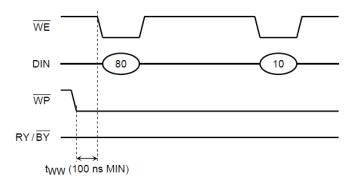

| tWW      | WP High to WE Low                                         | 100 | _   | ns   |  |  |  |

| tRR      | Ready to RE Falling Edge                                  | 20  | _   | ns   |  |  |  |

| tRW      | Ready to WE Falling Edge                                  | 20  | _   | ns   |  |  |  |

| tRP      | Read Pulse Width                                          | 12  | _   | ns   |  |  |  |

| tRC      | Read Cycle Time                                           | 25  | _   | ns   |  |  |  |

| tREA     | RE Access Time                                            | _   | 20  | ns   |  |  |  |

| tCEA     | CE Access Time                                            | _   | 25  | ns   |  |  |  |

| tCLR     | CLE Low to RE Low                                         | 10  | _   | ns   |  |  |  |

| tAR      | ALE Low to RE Low                                         | 10  | _   | ns   |  |  |  |

| tRHOH    | RE High to Output Hold Time                               | 25  | _   | ns   |  |  |  |

| tRLOH    | RE Low to Output Hold Time                                | 5   | _   | ns   |  |  |  |

| tRHZ     | RE High to Output High Impedance                          | -   | 60  | ns   |  |  |  |

| tCHZ     | CE High to Output High Impedance                          | _   | 20  | ns   |  |  |  |

| tCSD     | CE High to ALE or CLE Don't care                          | 0   | _   | ns   |  |  |  |

| tREH     | RE High Hold Time                                         | 10  | _   | ns   |  |  |  |

| tIR      | Output-High-impedance-to-RE Falling Edge                  | 0   | _   | ns   |  |  |  |

| tRHW     | RE High to WE Low                                         | 30  | _   | ns   |  |  |  |

| tWHC     | WE High to CE Low                                         | 30  | _   | ns   |  |  |  |

| tWHR     | WE High to RE Low                                         | 60  | _   | ns   |  |  |  |

| tR       | Memory Cell Array to Starting Address                     | -   | 25  | μs   |  |  |  |

| tDCBSYR1 | Data Cache Busy in Read Cache (following 31h and 3Fh)     | -   | 25  | μs   |  |  |  |

| tDCBSYR2 | Data Cache Busy in Page Copy (following 3Ah)              | -   | 30  | μs   |  |  |  |

| tWB      | WE High to Busy                                           | -   | 100 | ns   |  |  |  |

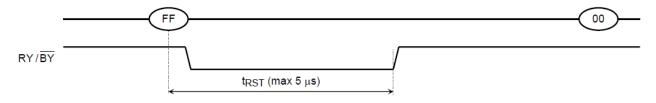

| tRST     | Device Reset Time (Ready/Read/Program/Erase) – 5/5/10/500 |     |     |      |  |  |  |

NOTE 1 tCLS and tALS cannot be shorter than tWP.

NOTE 2 tCS should be longer than tWP + 8ns.

### **AC Test Condition**

| Parameter                      | Condition              |  |  |

|--------------------------------|------------------------|--|--|

| Parameter                      | VCC : 1.70 to 1.95V    |  |  |

| Input level                    | VCC – 0.2 V, 0.2 V     |  |  |

| Input pulse rise and fall time | 3ns                    |  |  |

| Input comparison level         | Vcc / 2                |  |  |

| Output data comparison level   | Vcc / 2                |  |  |

| Output Load                    | 1 TTL GATE and CL=30pF |  |  |

NOTE 1 Busy to ready time depends on the pull-up resistor tied to the RY/BY pin.

# **Programming / Erasing Characteristics**

$(Ta = -25 \text{ to } 85^{\circ}\text{C}, V_{CC} = 1.70 \text{ to } 1.95\text{V})$

| Symbol                | Parameter                                           | Min | Тур. | Max | Unit  |

|-----------------------|-----------------------------------------------------|-----|------|-----|-------|

| tPROG                 | Average Programming Time                            | -   | 300  | 700 | μs    |

| tDCBSYW1              | Data Cache Busy Time in Write Cache (following 11h) | -   | _    | 10  | μs    |

| tDCBSYW2 <sup>1</sup> | Data Cache Busy Time in Write Cache (following 15h) | -   | _    | 700 | μs    |

| N                     | Number of Partial Program Cycles in the Same Page   | -   | _    | 4   | cycle |

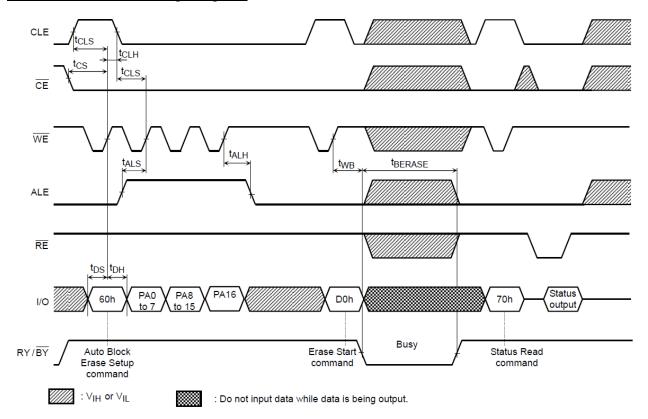

| tBERASE               | Block Erase Time                                    | _   | 3.5  | 10  | ms    |

NOTE 1 tDCBSYW2 depends on the timing between internal programming time and data in time.

## **Operation Mode: Logic and Command Tables**

The operation modes such as Program, Erase, Read and Reset are controlled by operations shown in command table. Address input, command input and data input/output are controlled by the CLE, ALE,  $\overline{\text{CE}}$ ,  $\overline{\text{WE}}$ ,  $\overline{\text{RE}}$  and  $\overline{\text{WP}}$  signals, as shown in Mode Selection Table.

### **Logic Table**

| CLE | ALE | CE | WE             | RE             | WP     | Mode                   |

|-----|-----|----|----------------|----------------|--------|------------------------|

| Н   | L   | L  | _ <b>_</b>     | Н              | *      | Command Input          |

| L   | L   | L  | _ <b>_</b>     | Н              | Н      | Data Input             |

| L   | Н   | L  | _ <b>_</b>     | Н              | *      | Address Input          |

| L   | L   | L  | Н              | <b></b>        | *      | Serial Data Output     |

| *   | *   | *  | *              | *              | Н      | During Program (Busy)  |

| *   | *   | *  | *              | *              | Н      | During Erase (Busy)    |

| *   | *   | Н  | *              | *              | *      | During Road (Russ)     |

| *   | *   | L  | H <sup>1</sup> | H <sup>1</sup> | *      | During Read (Busy)     |

| *   | *   | *  | *              | *              | L      | Program, Erase Inhibit |

| *   | *   | Н  | *              | *              | 0V/Vcc | Stand-by               |

H: VIH, L=VIL\*: VIH or VIL.

Note 1: If  $\overline{\text{CE}}$  is low during read busy.  $\overline{\text{WE}}$  and  $\overline{\text{RE}}$  must be held High to avoid unintended command/address input to device or read to device. Reset or Status Read command can be input during Read Busy.

### **Command Table**

| Function                                                | 1 <sup>st</sup> Cycle | 2 <sup>nd</sup> Cycle | Acceptable Command during Busy |

|---------------------------------------------------------|-----------------------|-----------------------|--------------------------------|

| Serial Data Input                                       | 80н                   | _                     |                                |

| Read                                                    | 00н                   | 30н                   |                                |

| Column Address Change in Serial Data Output             | 05н                   | Е0н                   |                                |

| Read with Data Cache                                    | 31н                   | _                     |                                |

| Read Start for Last Page in Read Cycle with Data Cache  | 3Fн                   | _                     |                                |

| Auto Page Program                                       | 80н                   | 10н                   |                                |

| Column Address Change in Serial Data Input              | 85н                   | _                     |                                |

| Auto Program with Data Cache                            | 80н                   | 15н                   |                                |

|                                                         | 80н                   | 11н                   |                                |

| Multi Page Program                                      | 81н                   | 15н                   |                                |

|                                                         | 81 <sub>H</sub>       | 10н                   |                                |

| Read for Page Copy (2) with Data Out                    | 00н                   | ЗАн                   |                                |

| Auto Program with Data Cache during Page Copy (2)       | 8Сн                   | 15н                   |                                |

| Auto Program for last page during Page Copy (2)         | 8Сн                   | 10н                   |                                |

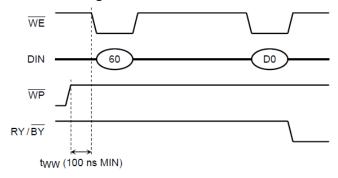

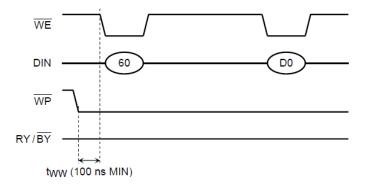

| Auto Block Erase                                        | 60н                   | D0н                   |                                |

| ID Read                                                 | 90н                   | _                     |                                |

| Status Read                                             | 70 <sub>H</sub>       | _                     | 0                              |

| Status Read for Multi-Page Program or Multi Block Erase | 71н                   | _                     | 0                              |

| Reset                                                   | FF <sub>H</sub>       | _                     | 0                              |

### Read mode operation states

|                 | CLE | ALE | CE | WE | RE | I/00 to I/07G  | Power  |

|-----------------|-----|-----|----|----|----|----------------|--------|

| Output Select   | L   | L   | L  | Н  | L  | Data output    | Active |

| Output Deselect | L   | L   | L  | Н  | Н  | High impedance | Active |

H: VIH, L=VIL

### **DEVICE OPERATION**

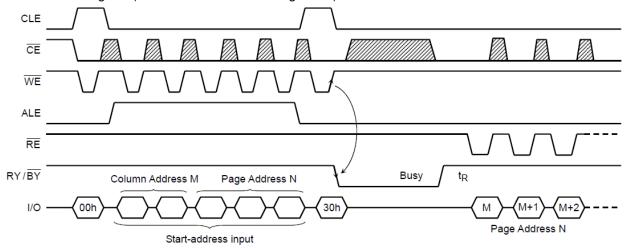

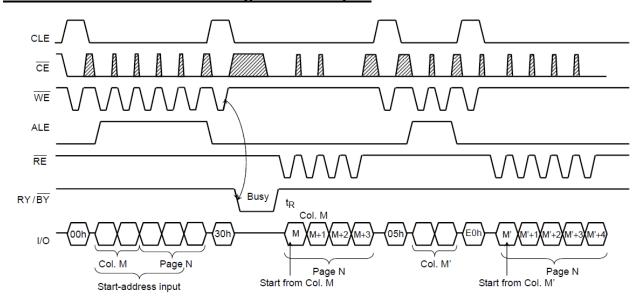

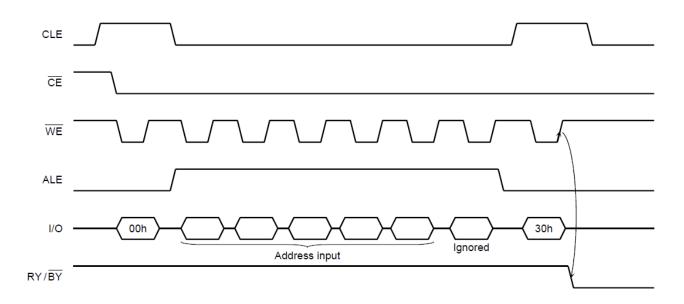

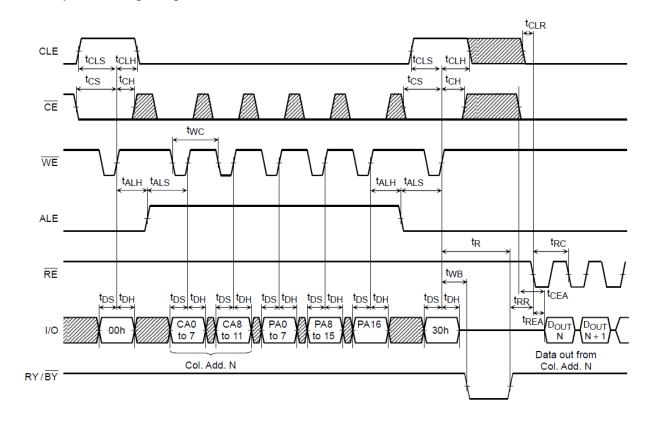

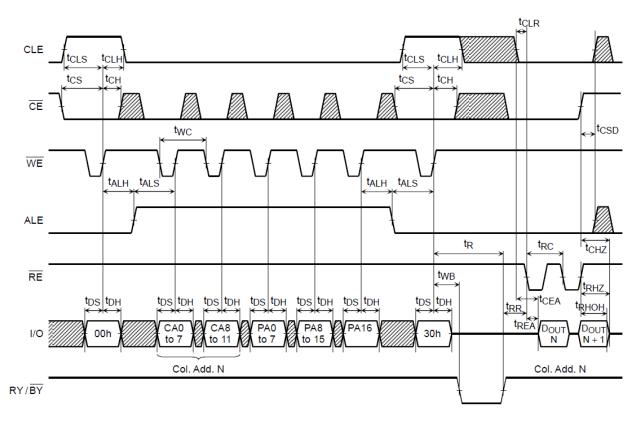

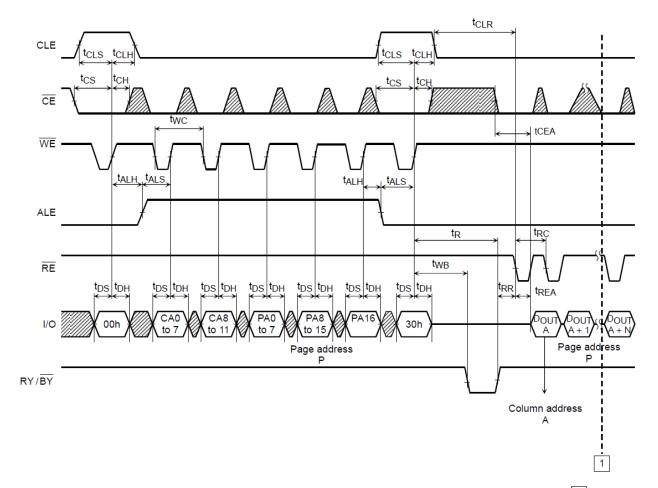

### **Read Mode**

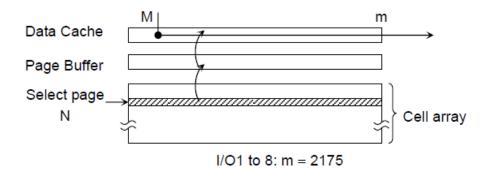

Read mode is set when the "00h" and "30h" commands are issued to the Command register. Between the two commands, a start address for the Read mode needs to be issued. Refer to the figures below for the sequence and the block diagram (Refer to the detailed timing chart.).

For X8:

A data transfer operation from the cell array to the Data Cache via Page Buffer starts on the rising edge of WE in the 30h command input cycle (after the address information has been latched). The device will be in the Busy state during this transfer period.

After the transfer period, the device returns to Ready state. Serial data can be output synchronously with the RE clock from the start address designated in the address input cycle.

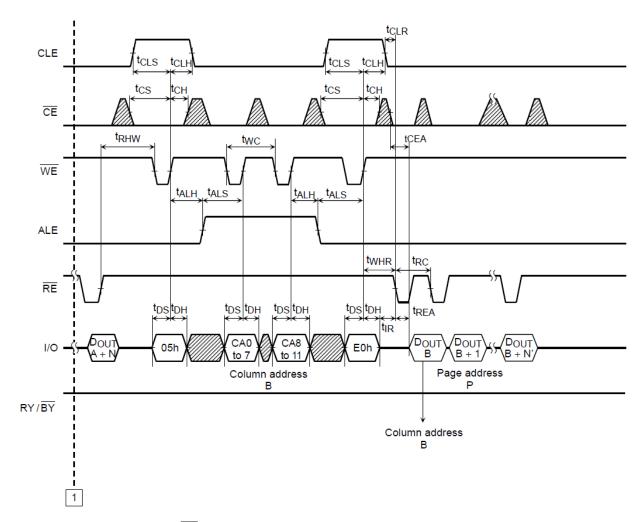

### Random Column Address Change in Read Cycle

During the serial data output from the Data Cache, the column address can be changed by inputting a new column address using the 05h and E0h commands. The data is read out in serial starting at the new column address. Random Column Address Change operation can be done multiple times within the same page.

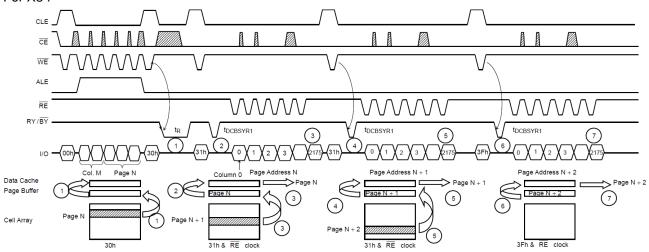

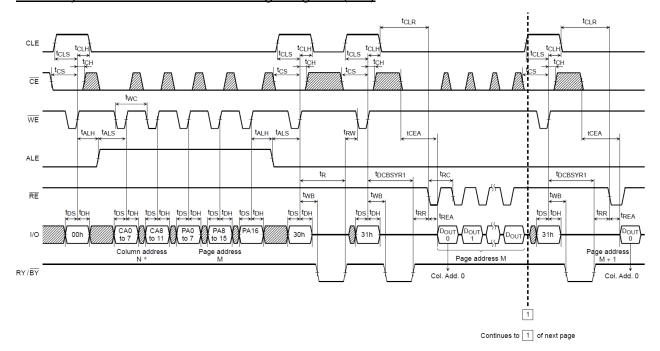

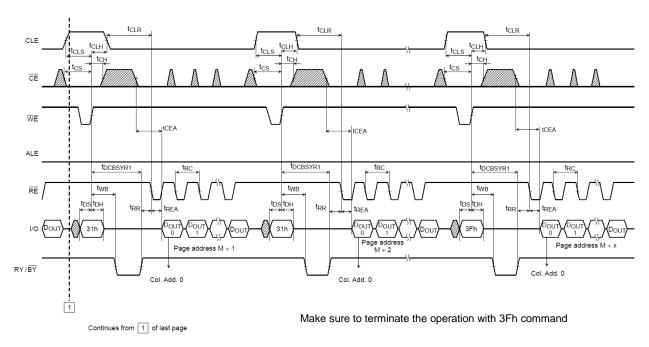

### **Read Operation with Read Cahe**

**√y∧** NM1282KSLAXAL

The device has a Read operation with Data Cache that enables the high speed read operation shown below. When the block address changes, this sequence has to be started from the beginning.

#### For X8:

If the 31h command is issued to the device, the data content of the next page is transferred to the Page Buffer during serial data out from the Data Cache, and therefore the tR (Data transfer from memory cell to data register) will be reduced.

- 1 Normal read. Data is transferred from Page N to Data Cache through Page Buffer. During this time period, the device outputs Busy state for tR max.

- 2 After the Ready/Busy returns to Ready, 31h command is issued and data is transferred to Data Cache from Page Buffer again. This data transfer takes tDCBSYR1 max and the completion of this time period can be detected by Ready/Busy signal.

- 3 Data of Page N + 1 is transferred to Page Buffer from cell while the data of Page N in Data cache can be read out by RE clock

- 4 The 31h command makes data of Page N + 1 transfer to Data Cache from Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tDCBSYR1 max.

- This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

- 5 Data of Page N + 2 is transferred to Page Buffer from cell while the data of Page N + 1 in Data cache can be read out by RE clock simultaneously.

- 6 The 3Fh command makes the data of Page N + 2 transfer to the Data Cache from the Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tDCBSYR1 max. This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

- 7 Data of Page N + 2 in Data Cache can be read out, but since the 3Fh command does not transfer the data from the memory cell to Page Buffer, the device can accept new command input immediately after the completion of serial data out.

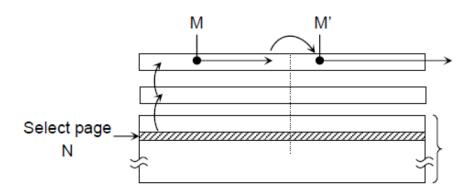

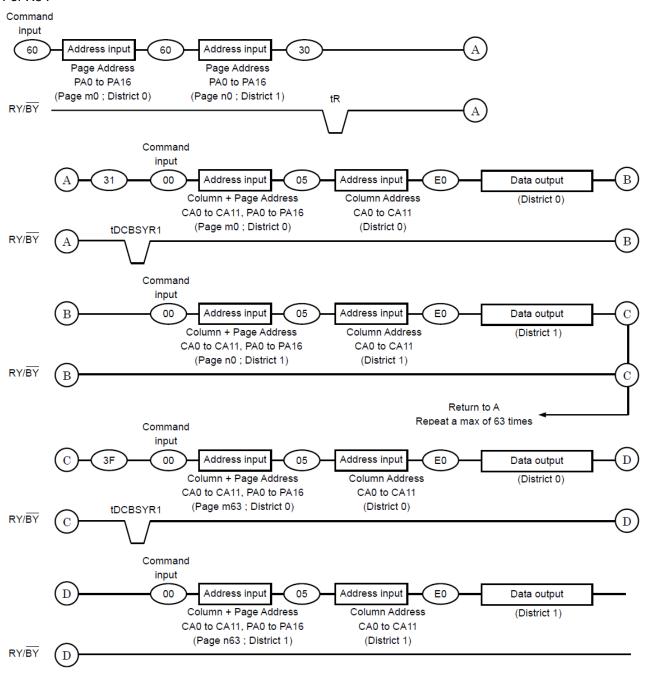

### **Multi Page Read Operation**

The device has a Multi Page Read operation and Multi Page Read with Data Cache operation.

### (1) Multi Page Read without Data Cache

The sequence of command and address input is shown below.

Same page address (PA0 to PA5) within each district has to be selected.

#### For X8:

The data transfer operation from the cell array to the Data Cache via Page Buffer starts on the rising edge of  $\overline{\text{WE}}$  in the 30h command input cycle (after the 2 Districts address information has been latched). The device will be in the Busy state during this transfer period.

After the transfer period, the device returns to Ready state. Serial data can be output synchronously with the RE clock from the start address designated in the address input cycle.

### NANUA NM1282KSLAXAL

#### (2) Multi Page Read with Data Cache

When the block address changes (increments) this sequenced has to be started from the beginning. The sequence of command and address input is shown below.

Same page address (PA0 to PA5) within each district has to be selected.

#### For X8:

#### (3) Notes

(a) Internal addressing in relation with the Districts

To use Multi Page Read operation, the internal addressing should be considered in relation with the District.

- The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046

District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

(b) Address input restriction for the Multi Page Read operation

There are following restrictions in using Multi Page Read;

(Restriction)

Maximum one block should be selected from each District.

Same page address (PA0 to PA5) within two districts has to be selected.

For example;

- (60) [District 0, Page Address 0x00000] (60) [District 1, Page Address 0x00040] (30)

- (60) [District 0, Page Address 0x00001] (60) [District 1, Page Address 0x00041] (30)

(Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

- (60) [District 0] (60) [District 1] (30)

- (60) [District 1] (60) [District 0] (30)

It requires no mutual address relation between the selected blocks from each District.

(c) WP signal

Make sure WP is held to High level when Multi Page Read operation is performed

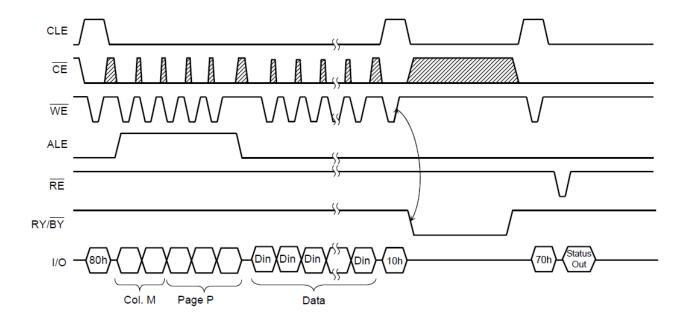

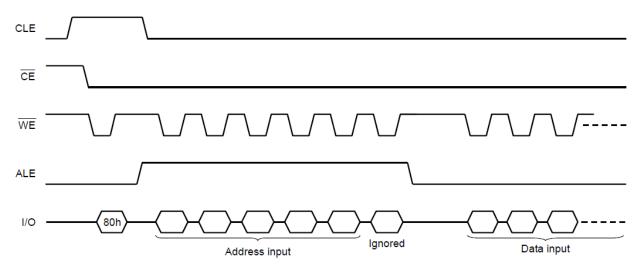

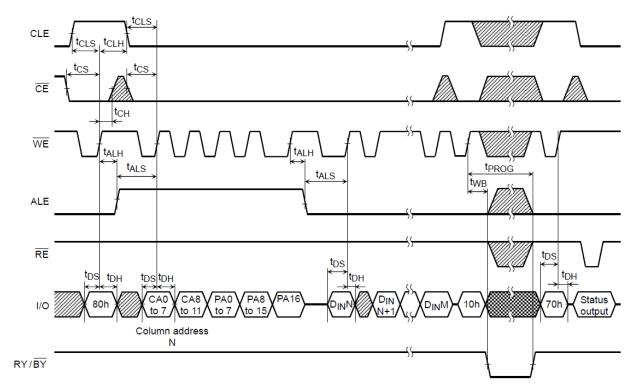

### **Auto Page Program Operation**

The device carries out an Automatic Page Program operation when it receives a "10h" Program command after the address and data have been input. The sequence of command, address and data input is shown below.

(Refer to the detailed timing chart.)

The data is transferred (programmed) from the Data Cache via the Page Buffer to the selected page on the rising edge of  $\overline{\text{WE}}$  following input of the "10h" command. After programming, the programmed data is transferred back to the Page Buffer to be automatically verified by the device.

If the programming does not succeed, the Program/Verify operation is repeated by the device until success is achieved or until the maximum loop number set in the device is reached.

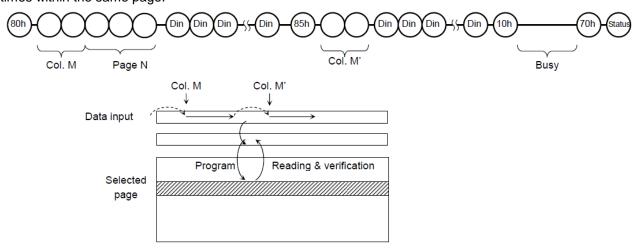

### Random Column Address Change in Auto Page Program Operation

The column address can be changed by the 85h command during the data input sequence of the Auto Page Program operation.

Two address input cycles after the 85h command are recognized as a new column address for the data input. After the new data is input to the new column address, the 10h command initiates the actual data program into the selected page automatically. The Random Column Address Change operation can be repeated multiple times within the same page.

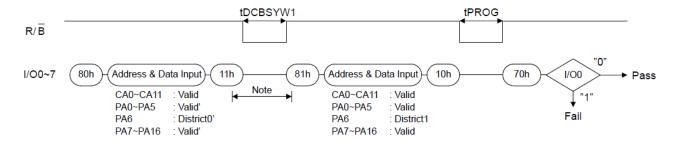

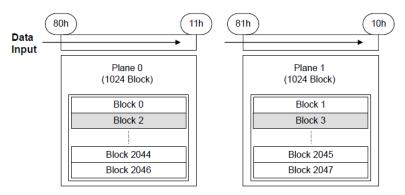

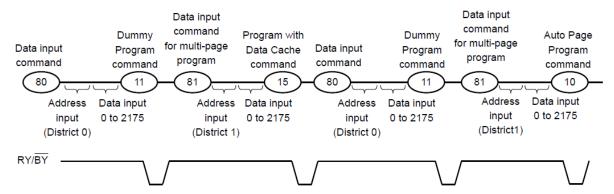

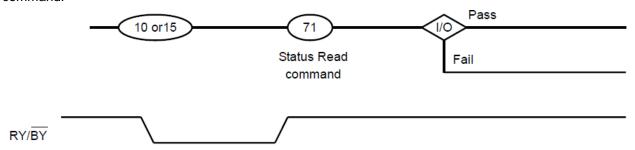

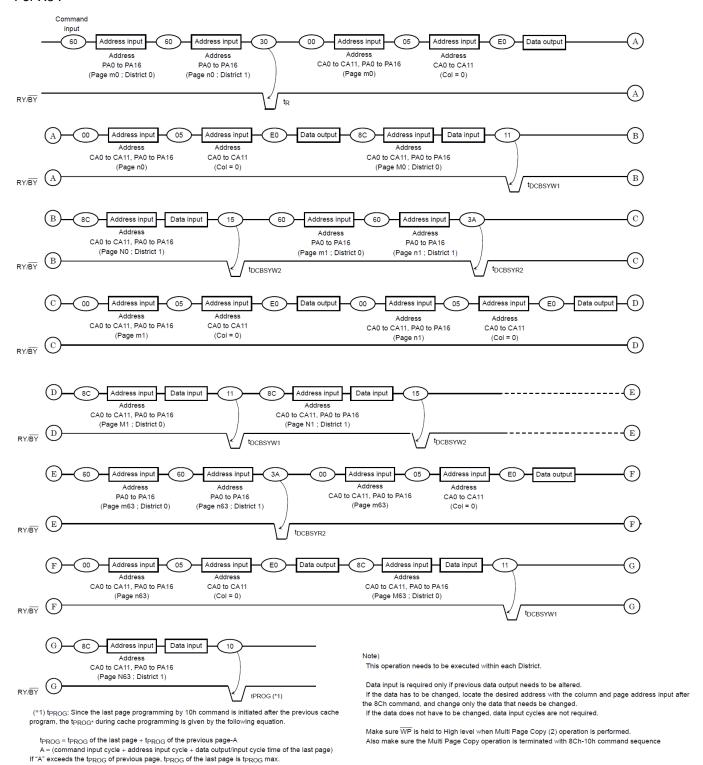

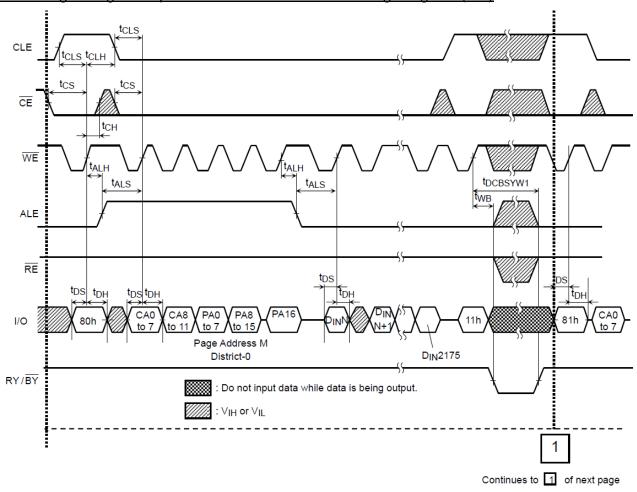

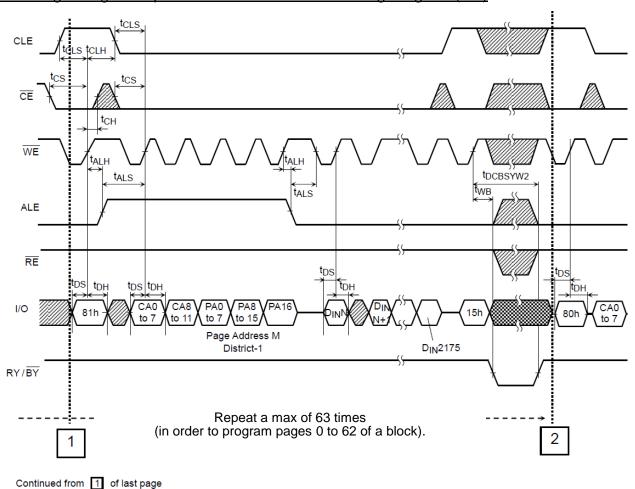

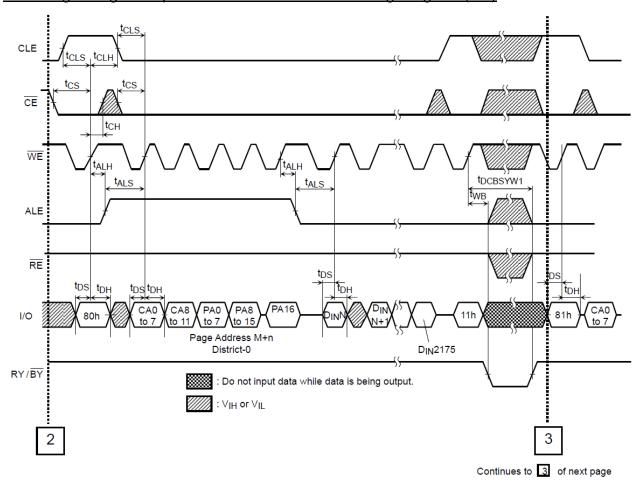

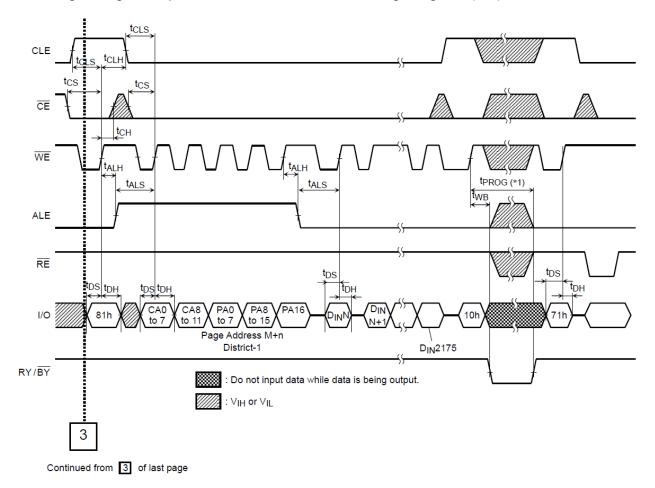

### Multi Page Program

The device has a Multi Page Program, which enables even higher speed program operation compared to Auto Page Program. The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.)

Although two planes are programmed simultaneously, pass/fail is not available for each page by "70h" command when the program operation completes. Status bit of I/O 1 is set to "1" when any of the pages fails. Limitation in addressing with Multi Page Program is shown below.

#### For X8:

NOTE: Any command between 11h and 81h is prohibited except 70h and FFh.

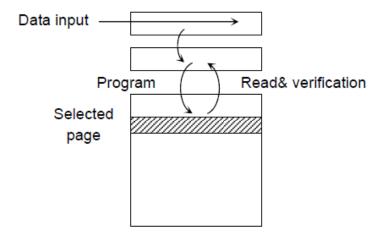

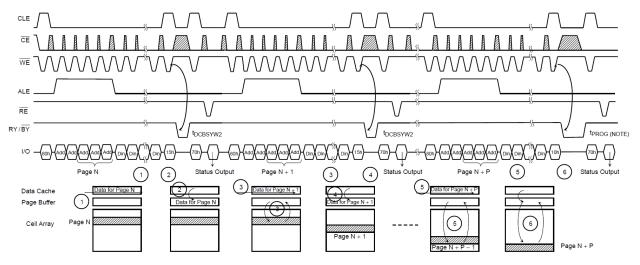

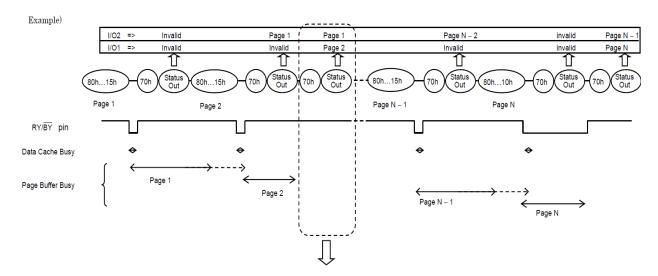

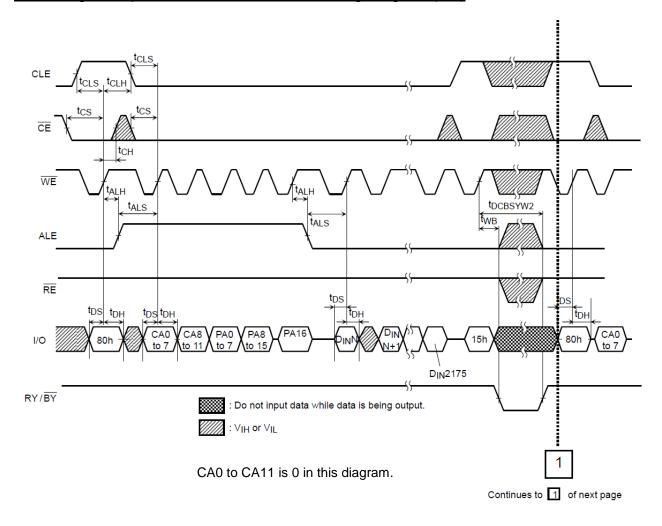

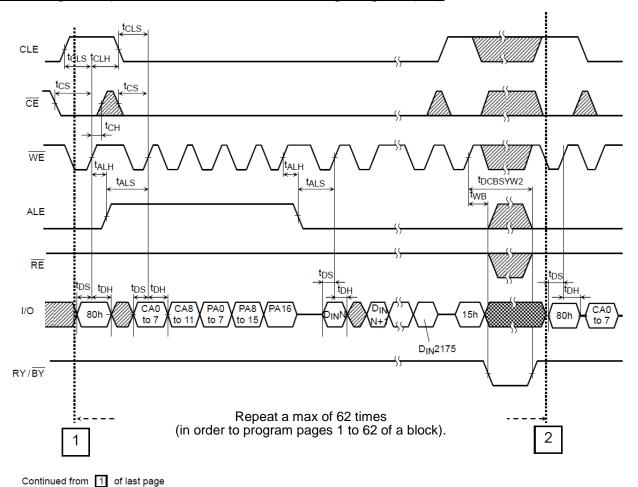

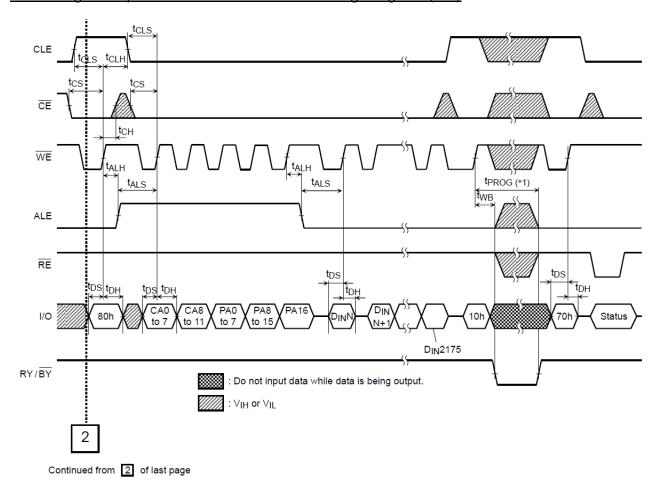

### **Auto Page Program Operation with Data Cache**

The device has an Auto Page Program with Data Cache operation enabling the high speed program operation shown below. When the block address changes this sequenced has to be started from the beginning.

Issuing the 15h command to the device after serial data input initiates the program operation with Data Cache

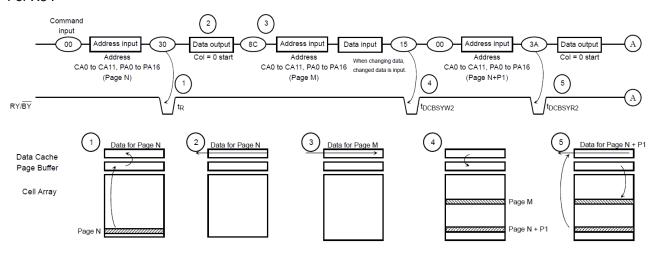

- 1 Data for Page N is input to Data Cache.

- 2 Data is transferred to the Page Buffer by the 15h command. During the transfer the Ready/Busy outputs Busy State (tDCBSYW2).

- 3 Data is programmed to the selected page while the data for page N + 1 is input to the Data Cache.

- 4 By the 15h command, the data in the Data Cache is transferred to the Page Buffer after the programming of page N is completed. The device output busy state from the 15h command until the Data Cache becomes empty. The duration of this period depends on timing between the internal programming of page N and serial data input for Page N + 1 (tDCBSYW2).

- 5 Data for Page N + P is input to the Data Cache while the data of the Page N + P 1 is being programmed.

- 6 The programming with Data Cache is terminated by the 10h command. When the device becomes Ready, it shows that the internal programming of the Page N + P is completed.

NOTE: Since the last page programming by the 10h command is initiated after the previous cache program, the tPROG during cache programming is given by the following;

tPROG = tPROG for the last page + tPROG of the previous page - ( command input cycle + address input cycle + data input cycle time of the last page)

Version 1.3 Nanya Technology Corp. 06/2018 All Rights Reserved. © Pass/fail status for each page programmed by the Auto Page Programming with Data Cache operation can be detected by the Status Read operation.

- I/O1: Pass/fail of the current page program operation.

- I/O2: Pass/fail of the previous page program operation.

The Pass/Fail status on I/O1 and I/O2 are valid under the following conditions.

- Status on I/O1: Page Buffer Ready/Busy is Ready State.

- The Page Buffer Ready/Busy is output on I/O6 by Status Read operation or RY / BY pin after the 10h command

- Status on I/O2: Data Cache Read/Busy is Ready State.

The Data Cache Ready/Busy is output on I/O7 by Status Read operation or RY / BY pin after the 15h command.

If the Page Buffer Busy returns to Ready before the next 80h command input, and if Status Read is done during this Ready period, the Status Read provides pass/fail for Page 2 on I/O1 and pass/fail result for Page1 on I/O2

Version 1.3 29 Nanya Technology Corp. 06/2018

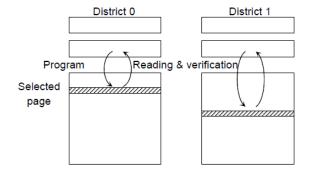

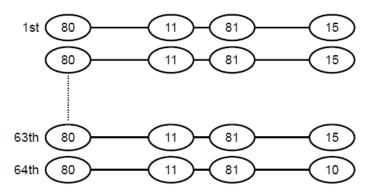

### Multi Page Program with Data Cache

The device has a Multi Page Program with Data Cache operation, which enables even higher speed program operation compared to Auto Page Program with Data Cache as shown below. When the block address changes (increments) this sequenced has to be started from the beginning.

The sequence of command, address and data input is shown below. (Refer to the detailed timing chart.) For X8:

After "15h" or "10h" Program command is input to device, physical programing starts as follows. For details of Auto Program with Data Cache, refer to "Auto Page Program with Data Cache".

The data is transferred (programmed) from the page buffer to the selected page on the rising edge of WE following input of the "15h" or "10h" command. After programming, the programmed data is transferred back to the register to be automatically verified by the device. If the programming does not succeed, the Program/Verify operation is repeated by the device until success is achieved or until the maximum loop number set in the device is reached.

Starting the above operation from 1st page of the selected erase blocks, and then repeating the operation total 64 times with incrementing the page address in the blocks, and then input the last page data of the blocks, "10h" command executes final programming. Make sure to terminate with 81h-10h- command sequence.

In this full sequence, the command sequence is following.

After the "15h" or "10h" command, the results of the above operation is shown through the "71h" Status Read command.

The 71<sub>H</sub> Command Status Description

| 1/0   | Status                                | Output                          |

|-------|---------------------------------------|---------------------------------|

| 1/0 0 | Chip Status1 : Pass / Fail            | Pass : 0 / Fail : 1             |

| I/O 1 | District 0 Chip Status1 : Pass / Fail | Pass : 0 / Fail : 1             |

| 1/0 2 | District 1 Chip Status2 : Pass / Fail | Pass : 0 / Fail : 1             |

| 1/0 3 | District 0 Chip Status1 : Pass / Fail | Pass : 0 / Fail : 1             |

| I/O 4 | District 1 Chip Status2 : Pass / Fail | Pass : 0 / Fail : 1             |

| 1/0 5 | Ready / Busy                          | Busy : 0 / Ready : 1            |

| I/O 6 | Data Cache Ready / Busy               | Busy : 0 / Ready : 1            |

| 1/0 7 | Write Protect                         | Protected: 0 / Not Protected: 1 |

I/O0 describes Pass/Fail condition of district 0 and 1 (OR data of I/O1 and I/O2). If one of the districts fails during multi page program operation, it shows "Fail".

I/O1 to I/O4 shows the Pass/Fail condition of each district. For details on "Chip Status 1" and "Chip Status2" refer to section "Status Read".

### Internal addressing in relation with the Districts

To use Multi Page Program operation, the internal addressing should be considered in relation with the District.

- · The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- · The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046

District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

### Address input restriction for the Multi Page Program with Data Cache operation

There are following restrictions in using Multi Page Program with Data Cache;

(Restriction)

Maximum one block should be selected from each District.

Same page address (PA0 to PA5) within two districts has to be selected.

For example;

(80) [District 0, Page Address 0x00000] (11) (81) [District 1, Page Address 0x00040] (15 or 10)

(80) [District 0, Page Address 0x00001] (11) (81) [District 1, Page Address 0x00041] (15 or 10)

(Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(80) [District 0] (11) (81) [District 1] (15 or 10)

(80) [District 1] (11) (81) [District 0] (15 or 10)

It requires no mutual address relation between the selected blocks from each District.

### Operating restriction during the Multi Page Program with Data Cache operation

(Restriction)

The operation has to be terminated with "10h" command.

Once the operation is started, no commands other than the commands shown in the timing diagram is allowed to be input except for Status Read command and reset command.

NM1282KSLAXAL

# Page Copy (2)

By using Page Copy (2), data in a page can be copied to another page after the data has been read out.

When the block address changes (increments) this sequenced has to be started from the beginning.

#### For X8:

Page Copy (2) operation is as following.

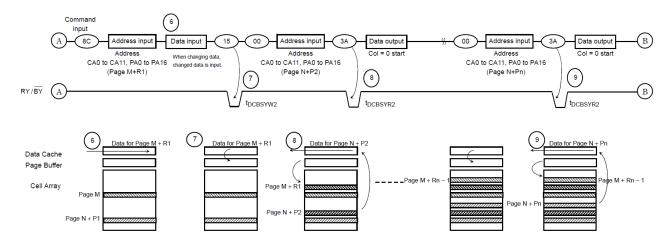

- 1 Data for Page N is transferred to the Data Cache.

- 2 Data for Page N is read out.

- 3 Copy Page address M is input and if the data needs to be changed, changed data is input.

- 4 Data Cache for Page M is transferred to the Page Buffer.

- 5 After the Ready state, Data for Page N + P1 is output from the Data Cache while the data of Page M is being programmed.

NM1282KSLAXAL

### For X8:

- 6 Copy Page address (M + R1) is input and if the data needs to be changed, changed data is input.

- 7 After programming of page M is completed, Data Cache for Page M + R1 is transferred to the Page Buffer.

- 8 By the 15h command, the data in the Page Buffer is programmed to Page M + R1. Data for Page N + P2 is transferred to the Data cache.

- 9 The data in the Page Buffer is programmed to Page M + Rn 1. Data for Page N + Pn is transferred to the Data Cache.

#### For X8:

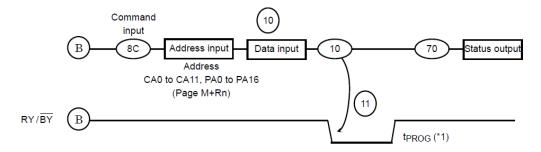

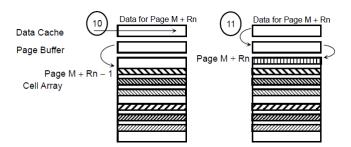

10 Copy Page address (M + Rn) is input and if the data needs to be changed, changed data is input.

11 By issuing the 10h command, the data in the Page Buffer is programmed to Page M + Rn.

(\*1) Since the last page programming by the 10h command is initiated after the previous cache program, the tPROG here will be expected as the following,

tPROG = tPROG of the last page + tPROG of the previous page - ( command input cycle + address input cycle + data output/input cycle time of the last page)

NOTE) This operation needs to be executed within District-0 or District-1.

Data input is required only if previous data output needs to be altered.

If the data has to be changed, locate the desired address with the column and page address input after the 8Ch command, and change only the data that needs be changed.

If the data does not have to be changed, data input cycles are not required.

Make sure  $\overline{WP}$  is held to High level when Page Copy (2) operation is performed.

Also make sure the Page Copy operation is terminated with 8Ch-10h command sequence

### Mutil Page Copy (2)

NANYA NM1282KSLAXAL

By using Multi Page Copy (2), data in two pages can be copied to other pages after the data has been read out. When each block address changes (increments) this sequence has to be started from the beginning. Same page address (PA0 to PA5) within two districts has to be selected.

#### For X8:

Version 1.3 36 Nanya Technology Corp. All Rights Reserved. ©

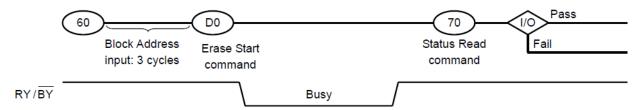

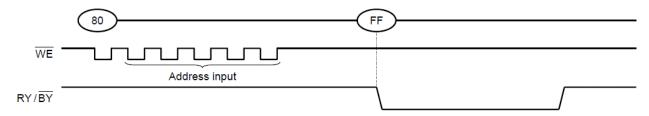

## **Auto Block Erase**

The Auto Block Erase operation starts on the rising edge of WE after the Erase Start command "D0h" which follows the Erase Setup command "60h". This two-cycle process for Erase operations acts as an extra layer of protection from accidental erasure of data due to external noise. The device automatically executes the Erase and Verify operations.

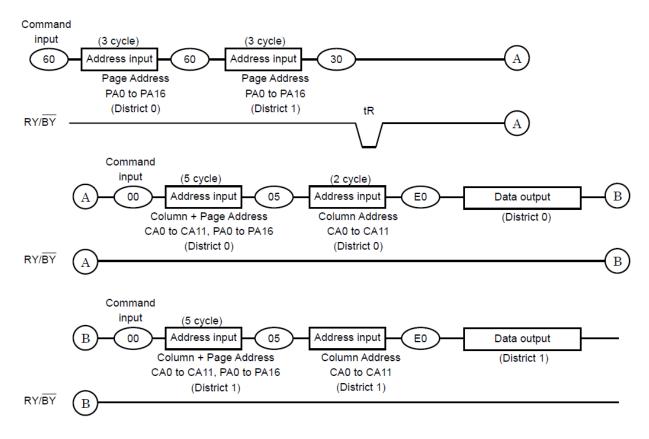

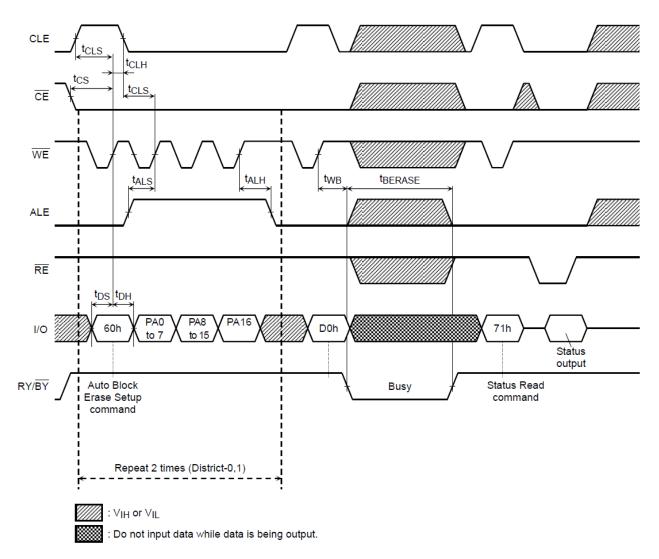

# **Multi Block Erase**

The Multi Block Erase operation starts by selecting two block addresses before D0h command as in below diagram. The device automatically executes the Erase and Verify operations and the result can be monitored by checking the status by 71h status read command. For details on 71h status read command, refer to section "Multi Page Program with Data Cache".

## Internal addressing in relation with the Districts

To use Multi Block Erase operation, the internal addressing should be considered in relation with the District.

- · The device consists from 2 Districts.

- Each District consists from 1024 erase blocks.

- · The allocation rule is follows.

District 0: Block 0, Block 2, Block 4, Block 6,..., Block 2046

District 1: Block 1, Block 3, Block 5, Block 7,..., Block 2047

### Address input restriction for the Multi Block Erase

There are following restrictions in using Multi Block Erase

(Restriction)

Maximum one block should be selected from each District.

For example;

(60) [District 0] (60) [District 1] (D0)

(Acceptance)

There is no order limitation of the District for the address input.

For example, following operation is accepted;

(60) [District 1] (60) [District 0] (D0)

It requires no mutual address relation between the selected blocks from each District.

Make sure to terminate the operation with D0h command. If the operation needs to be terminated before D0h command input, input the FFh reset command to terminate the operation.

Version 1.338Nanya Technology Corp.06/2018All Rights Reserved. ©

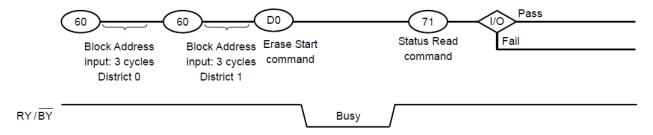

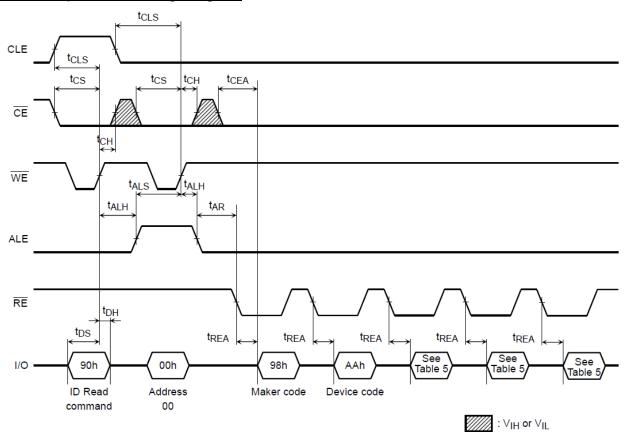

# **ID Read**

The device contains ID codes which can be used to identify the device type, the manufacturer, and features of the device. The ID codes can be read out under the following timing conditions:

# **ID Definition Table (X8)**

|                      | Description                      |   | 1/06 | 1/05 | I/O4 | 1/03 | 1/02 | I/01 | 1/00 | Hex Data        |

|----------------------|----------------------------------|---|------|------|------|------|------|------|------|-----------------|

| 1 <sup>st</sup> Data | Maker Code                       |   | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 98н             |

| 2 <sup>nd</sup> Data | Device Code                      | 1 | 0    | 1    | 0    | 1    | 0    | 1    | 0    | $AA_H$          |

| 3 <sup>rd</sup> Data | Chip Number, Cell Type           |   | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 90 <sub>H</sub> |

| 4 <sup>th</sup> Data | Page Size, Block Size, I/O Width | 0 | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 15н             |

| 5 <sup>th</sup> Data | Plane Number                     |   | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 76н             |

### 3rd ID Data

| Item                 | Description   | 1/07 | 1/06 | 1/05 | 1/04 | 1/03 | 1/02 | I/O1 | 1/00 |

|----------------------|---------------|------|------|------|------|------|------|------|------|

|                      | 1             |      |      |      |      |      |      | 0    | 0    |

| Internal Chip Number | 2             |      |      |      |      |      |      | 0    | 1    |

|                      | 4             |      |      |      |      |      |      | 1    | 0    |

|                      | 8             |      |      |      |      |      |      | 1    | 1    |

|                      | 2 Level Cell  |      |      |      |      | 0    | 0    |      |      |

| Call Time            | 4 Level Cell  |      |      |      |      | 0    | 1    |      |      |

| Cell Type            | 8 Level Cell  |      |      |      |      | 1    | 0    |      |      |

|                      | 16 Level Cell |      |      |      |      | 1    | 1    |      |      |

| Reserved             |               | 1    | 0    | 0    | 1    |      |      |      |      |

# 4th ID Data

| Item                     | Description | I/07 | I/O6 | 1/05 | 1/04 | 1/03 | 1/02 | I/O1 | 1/00 |

|--------------------------|-------------|------|------|------|------|------|------|------|------|

|                          | 1 KB        |      |      |      |      |      |      | 0    | 0    |

| Page Size                | 2 KB        |      |      |      |      |      |      | 0    | 1    |

| (without redundant area) | 4 KB        |      |      |      |      |      |      | 1    | 0    |

|                          | 8 KB        |      |      |      |      |      |      | 1    | 1    |

|                          | 64 KB       |      |      | 0    | 0    |      |      |      |      |

| Block Size               | 128 KB      |      |      | 0    | 1    |      |      |      |      |

| (without redundant area) | 256 KB      |      |      | 1    | 0    |      |      |      |      |

|                          | 512 KB      |      |      | 1    | 1    |      |      |      |      |

| I/O Width                | X8          |      | 0    |      |      |      |      |      |      |

| I/O VVIGITI              | X16         |      | 1    |      |      |      |      |      |      |

| Reserved                 |             | 0    |      |      |      | 0    | 1    |      |      |

# 5th ID Data

| Item         | Description | 1/07 | 1/06 | 1/05 | 1/04 | 1/03 | 1/02 | I/O1 | 1/00 |

|--------------|-------------|------|------|------|------|------|------|------|------|

|              | 1 Plane     |      |      |      |      | 0    | 0    |      |      |

| Plane Number | 2 Plane     |      |      |      |      | 0    | 1    |      |      |

|              | 4 Plane     |      |      |      |      | 1    | 0    |      |      |

|              | 8 Plane     |      |      |      |      | 1    | 1    |      |      |

| Reserved     |             | 0    | 1    | 1    | 1    |      |      | 1    | 0    |

NUA NM1282KSLAXAL

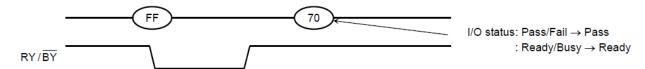

# Status Read

The device automatically implements the execution and verification of the Program and Erase operations. The status Read function is used to monitor the Ready/Busy status of the device, determine the result (pass/fail) of a Program or Erase operation, and determine whether the device is in Protect mode. The device status is output via the I/O port using RE after a "70h" command input. The Status Read can also be used during a Read operation to find out the Ready/Busy status.

# Status Register Definition for 70<sub>H</sub> Command

| 1/0   | Page Program  | Block Erase   | Read            | Cache Read    | Cache Program | Definition                                         |

|-------|---------------|---------------|-----------------|---------------|---------------|----------------------------------------------------|

| 1/0 0 | Pass / Fail   | Pass / Fail   | Invalid Invalid |               | Pass / Fail   | Chip Status1<br>Pass : 0 / Fail : 1                |

| I/O 1 | Invalid       | Invalid       | Invalid         | Invalid       | Pass / Fail   | Chip Status2<br>Pass : 0 / Fail : 1                |

| 1/0 2 | 0             | 0             | 0               | 0             | 0             | Not Used                                           |

| 1/03  | 0             | 0             | 0               | 0             | 0             | Not Used                                           |

| 1/0 4 | 0             | 0             | 0               | 0             | 0             | Not Used                                           |

| 1/0 5 | Ready / Busy  | Ready / Busy  | Ready / Busy    | Ready / Busy  | Ready / Busy  | Page Buffer<br>Busy: 0 / Ready: 1                  |

| 1/0 6 | Ready / Busy  | Ready / Busy  | Ready / Busy    | Ready / Busy  | Ready / Busy  | Data Cache<br>Busy: 0 / Ready: 1                   |

| 1/07  | Write Protect | Write Protect | Write Protect   | Write Protect | Write Protect | Write Prot<br>Protected : 0<br>/ Not Protected : 1 |

The Pass/Fail status on I/O0 and I/O1 is only valid during a Program/Erase operation when the device is in the NOTE Ready state.

#### Chip Status 1:

During a Auto Page Program or Auto Block Erase operation this bit indicates the pass/fail result.

During a Auto Page Programming with Data Cache operation, this bit shows the pass/fail results of the current page program operation, and therefore this bit is only valid when I/O5 shows the Ready state.

#### Chip Status 2:

This bit shows the pass/fail result of the previous page program operation during Auto Page Programming with Data Cache. This status is valid when I/O6 shows the Ready State.

The status output on the I/O5 is the same as that of I/O6 if the command input just before the 70h is not 15h or 31h.

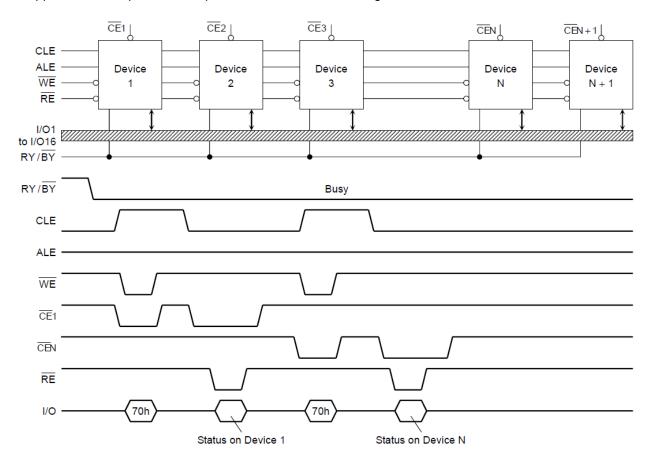

An application example with multiple devices is shown in the figure below.

System Design Note: If the  $\overline{RY}$  /  $\overline{BY}$  pin signals from multiple devices are wired together as shown in the diagram, the Status Read function can be used to determine the status of each individual device.

#### Reset

The Reset mode stops all operations. For example, in case of a Program or Erase operation, the internally generated voltage is discharged to 0 volt and the device enters the Wait state.

Reset during a Cache Program/Page Copy may not just stop the most recent page program but it may also stop the previous program to a page depending on when the FF reset is input.

The response to a "FFh" Reset command input during the various device operations is as follows:

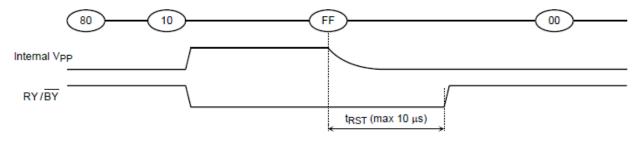

### When a Reset (FFh) command is input during programming

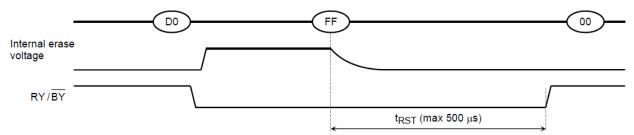

### When a Reset (FFh) command is input during erasing

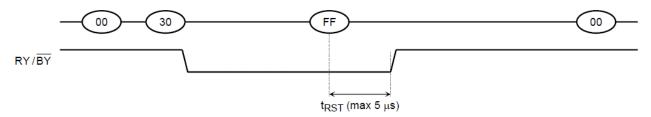

### When a Reset (FFh) command is input during Read operation

### When a Reset (FFh) command is input during Ready

### When a Status Read command (70h) is input after a Reset

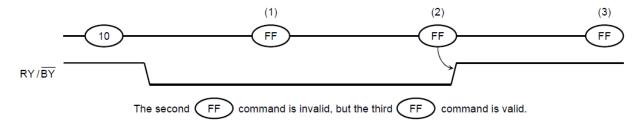

#### When two or more Reset commands are input in succession

# APPLICATION NOTES AND COMMENTS

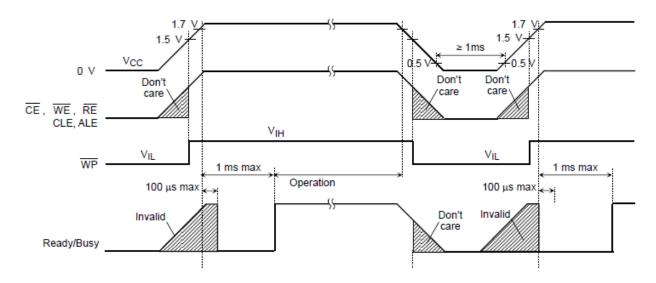

## (1)Power-on/off sequence

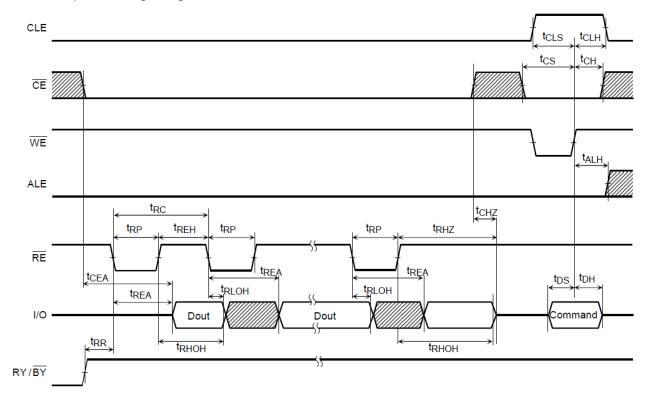

The timing sequence shown in the figure below is necessary for the power-on/off sequence.

The device internal initialization starts after the power supply reaches an appropriate level in the power on sequence.

During the initialization the device Ready/Busy signal indicates the Busy state as shown in the figure below. In this time period, the acceptable commands are FFh or 70h.

The WP signal is useful for protecting against data corruption at power-on/off.

(2) Do not turn off the power before write/erase operation is complete. Avoid using the device when the battery is low. Power shortage and/or power failure before write/erase operation is complete will cause loss of data and/or damage to data.

## (3)Power-on Reset

The following sequence is necessary because some input signals may not be stable at power-on.

# (4)Prohibition of unspecified commands

The operation commands are listed in Logic Table. Input of a command other than those specified in Logic Table is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

# (5)Restriction of commands while in the Busy state

During the Busy state, do not input any command except 70h(71h) and FFh.

## (6)Acceptable commands after Serial Input command "80h"

Once the Serial Input command "80h" has been input, do not input any command other than the Column Address Change in Serial Data Input command "85h", Auto Program command "10h", Multi Page Program command "11h", Auto Program with Data Cache Command "15h", or the Reset command "FFh".

If a command other than "85h", "10h", "11h", "15h" or "FFh" is input, the Program operation is not performed and the device operation is set to the mode which the input command specifies.

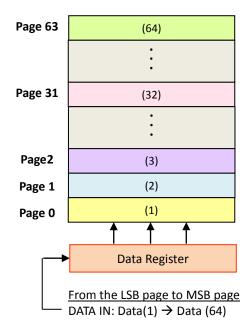

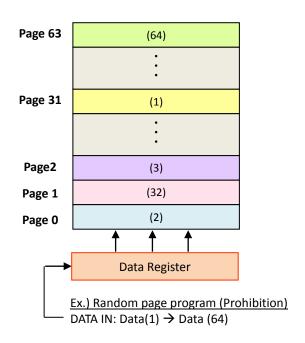

## (7)Addressing for Program Operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most significant bit) page of the block. Random page address programming is prohibited.

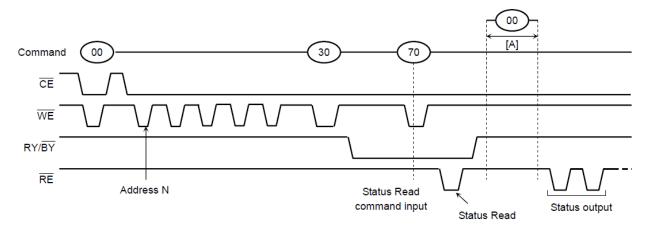

# (8)Status Read during a Read operation

The device status can be read out by inputting the Status Read command "70h" in Read mode. Once the device has been set to Status Read mode by a "70h" command, the device will not return to Read mode unless the Read command "00h" is inputted during [A]. If the Read command "00h" is inputted during [A], Status Read mode is reset, and the device returns to Read mode. In this case, data output starts automatically from address N and address input is unnecessary

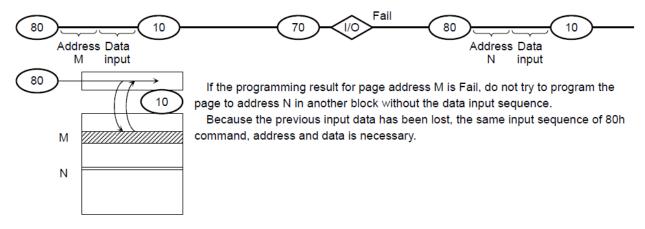

## (9) Auto programming failure

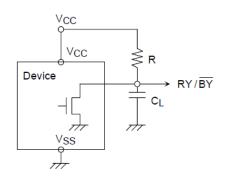

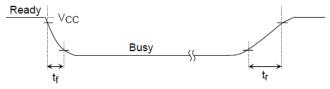

# (10)RY / $\overline{BY}$ : termination for the Ready/Busy pin (RY / $\overline{BY}$ )

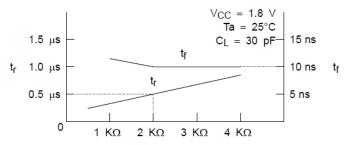

A pull-up resistor needs to be used for termination because the RY /  $\overline{\text{BY}}$  buffer consists of an open drain circuit.

This data may vary from device to device. We recommend that you use this data as a reference when selecting a resistor value.

# (11)Note regarding the $\overline{\text{WP}}$ signal

The Erase and Program operations are automatically reset when WP goes Low. The operations are enabled and disabled as follows:

### **Enable Programming**

### **Disable Programming**

#### **Enable Erasing**

#### **Disable Erasing**

## (12)When six address cycles are input

Although the device may read in a sixth address, it is ignored inside the chip.

## **Read operation**

### **Program operation**

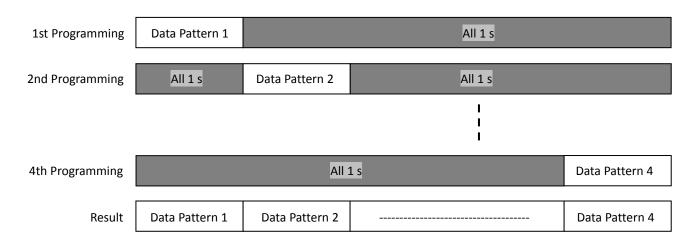

# (13)Several programming cycles on the same page (Partial Page Program)

Each segment can be programmed individually as follows:

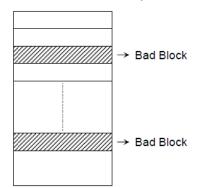

# (14)Invalid blocks (bad blocks)

The device occasionally contains unusable blocks. Therefore, the following issues must be recognized:

Please do not perform an erase operation to bad blocks. It may be impossible to recover the bad block information if the information is erased.

Check if the device has any bad blocks after installation into the system.

Refer to the test flow for bad block detection. Bad blocks which are detected by the test flow must be managed as unusable blocks by the system.

A bad block does not affect the performance of good blocks because it is isolated from the bit lines by select gates.

#### The number of valid blocks over the device lifetime is as follows:

| Symbol                   | Min   | Тур. | Max   | Unit   |

|--------------------------|-------|------|-------|--------|

| Valid(Good) Block Number | 2,008 | _    | 2,048 | Blocks |

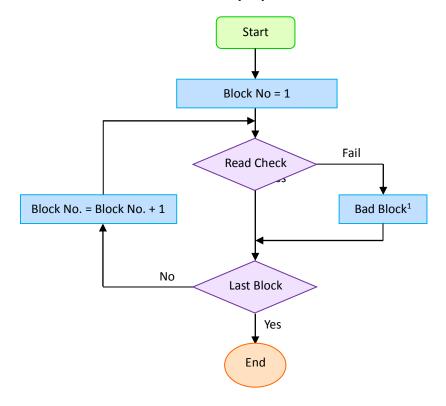

#### **Bad Block Test Flow**

Regarding invalid blocks, bad block mark is in whole pages.

Please read one column of any page in each block. It makes sure that every invalid block has Majority "0" data at this column. If the data of the column is Majority "0", define the block as a bad block.

Note1: No erase operation is allowed to detected bad blocks.

### (15) Failure phenomena for Program and Erase Operations

The device may fail during a Program or Erase operation.

The following possible failure modes should be considered when implementing a highly reliable system.

| Failure Mode |                     | Detection and Countermeasure Sequence         |

|--------------|---------------------|-----------------------------------------------|

| Block        | Erase Failure       | Read Status after Erase → Block Replacement   |

| Page         | Programming Failure | Read Status after Program → Block Replacement |

| Read         | Bit Error           | ECC Correction / Block Refresh                |

NOTE 1 ECC: Error Correction Code. 8 bit correction per 512 Bytes is necessary.

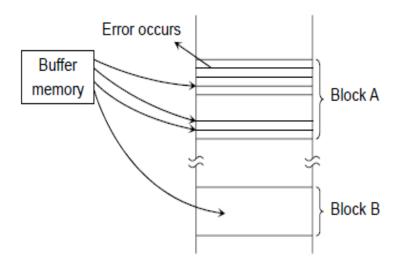

### **Block Replacement**

### **Program**

When an error happens in Block A, try to reprogram the data into another Block (Block B) by loading from an external buffer. Then, prevent further system accesses to Block A (by creating a bad block table or by using another appropriate scheme).

#### **Erase**

When an error occurs during an Erase operation, prevent future accesses to this bad block (again by creating a table within the system or by using another appropriate scheme).

(16) The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

## (17) Reliability Guidance

This reliability guidance is intended to notify some guidance related to using NAND flash with 8bit ECC for each 512 bytes. For detailed reliability data, please refer to TOSHIBA's reliability note.

Although random bit errors may occur during use, it does not necessarily mean that a block is bad.

Generally, a block should be marked as bad when a program status failure or erase status failure is detected.

The other failure modes may be recovered by a block erase.

ECC treatment for read data is mandatory due to the following Data Retention and Read Disturb failures.

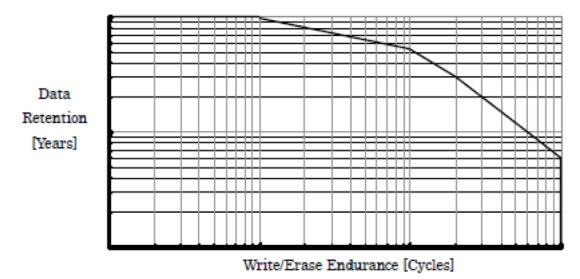

#### ■ Write/Erase Endurance

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

#### ■ Data Retention

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erasure and reprogramming, the block may become usable again.

Here is the combined characteristics image of Write/Erase Endurance and Data Retention.

#### ■ Read Disturb

A read operation may disturb the data in memory. The data may change due to charge gain. Usually, bit errors occur on other pages in the block, not the page being read. After a large number of read cycles (between block erases), a tiny charge may build up and can cause a cell to be soft programmed to another state. After block erasure and reprogramming, the block may become usable again.

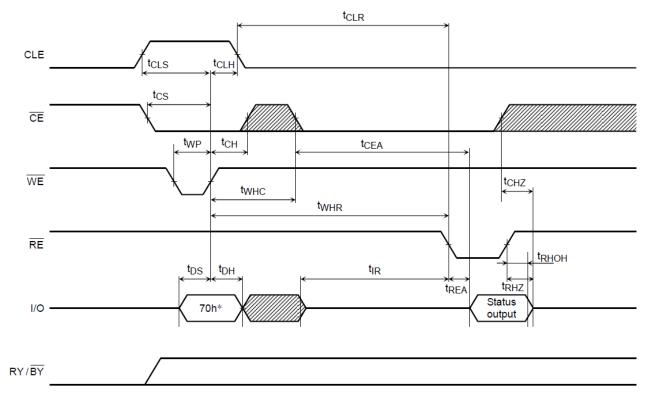

#### **TIMING DIAGRAMS**

# Latch Timing Diagram for Command/Address/Data

# Command Input Cycle Timing Diagram

# Address Input Cycle Timing Diagram

# **Data Input Cycle Timing Diagram**

# Serial Read Cycle Timing Diagram